コプレーナ導波路(CPW)の電磁界シミュレーション

理論と物理

CPWの基本構造

コプレーナ導波路ってマイクロストリップと何が違うんですか? どっちも基板上の伝送線路ですよね?

大きな違いはGND面の位置だ。マイクロストリップは基板裏面にGNDがあるけど、CPWは信号線の両側にGNDを同一面に配置する。断面を見ると「GND — ギャップ — 信号線 — ギャップ — GND」というG-S-G構造になっている。

同じ面にGNDがあると、何がうれしいんですか?

実務的なメリットは3つある。

- ビア不要 — GNDが表面にあるので、裏面への接続ビアが要らない。MMICやRFICで部品実装がシンプルになる

- プローブ測定が容易 — G-S-Gプローブをそのまま当てられるから、オンウェハー測定の標準構造として使われている

- 分散が小さい — 準TEMモードで伝搬するため、マイクロストリップより周波数分散が小さく、広帯域設計に向く

1969年にC.P.Wenが発明して以来、GaAsやInPの化合物半導体回路では事実上の標準構造だ。最近は5Gミリ波の28/39 GHz帯フロントエンドでも多用されている。

CPWの断面構造を定義するパラメータは以下のとおりである。

| パラメータ | 記号 | 説明 | 典型値 |

|---|---|---|---|

| 信号線幅 | $w$ | 中央導体の幅 | 10〜500 μm |

| ギャップ幅 | $s$ | 信号線とGND間の間隔 | 5〜200 μm |

| 基板厚さ | $h$ | 誘電体基板の厚さ | 100〜635 μm |

| 導体厚さ | $t$ | メタライゼーション厚さ | 0.5〜5 μm |

| 比誘電率 | $\varepsilon_r$ | 基板の誘電率 | 2.2(PTFE)〜12.9(GaAs) |

特性インピーダンスと楕円積分

CPWの特性インピーダンスって、マイクロストリップみたいに経験式で求めるんですか?

いや、CPWの場合は第1種完全楕円積分 $K(k)$ を使った解析的な式がある。共形写像法(conformal mapping)から導出されるんだ。

無限厚基板上のCPW(裏面GNDなし)の特性インピーダンスは次式で与えられる。

ここで各変数は以下のように定義される。

- $w$:信号線幅、$s$:ギャップ幅

- $K(k)$:第1種完全楕円積分 $\displaystyle K(k) = \int_0^{\pi/2} \frac{d\theta}{\sqrt{1 - k^2 \sin^2\theta}}$

- $k'$:$k$ の補パラメータ

楕円積分って初めて見ました…。実際の設計で毎回これを手計算するんですか?

手計算はしない。$K(k)/K(k')$ の比には便利な近似式があって、実務ではこちらを使うことが多い。

$K(k)/K(k')$ の近似(Hilberg近似):

この近似の誤差は全域で0.01%以下であり、電卓レベルの計算でも十分な精度が得られる。

導出の背景:共形写像法

CPWの特性インピーダンス公式は、Schwarz-Christoffel変換という共形写像を用いて導出される。CPW断面($z$平面)の電極配置を、平行平板コンデンサ($w$平面)に写像することで、単位長さあたりのキャパシタンス $C$ を解析的に求められる。$Z_0 = 1/(v_p \cdot C)$ の関係から特性インピーダンスが得られる。共形写像が使える理由は、CPWが準TEM構造であり2Dラプラス方程式で電位分布を記述できるからだ。

実効誘電率

CPWの電界は基板内と空気中の両方に分布するため、実効誘電率は基板の比誘電率 $\varepsilon_r$ と空気($\varepsilon_r = 1$)の加重平均となる。

ここで $k_1$ は基板厚さ $h$ を考慮した修正パラメータである。

基板が薄いと実効誘電率は変わるんですか?

変わる。基板が薄くなると電界が空気側により多く漏れ出すので、$\varepsilon_{\text{eff}}$ は $\varepsilon_r$ から離れて1に近づく。逆に基板が十分厚い($h \gg w + 2s$)と $k_1 \to k$ となって、無限厚基板の近似 $\varepsilon_{\text{eff}} \approx (\varepsilon_r + 1)/2$ に収束する。例えばアルミナ基板($\varepsilon_r = 9.8$)で $h = 635\,\mu\text{m}$、$w = 50\,\mu\text{m}$ だと $\varepsilon_{\text{eff}} \approx 5.4$ 程度になるよ。

損失メカニズム

CPWの損失って、どういう要因で決まるんですか? ミリ波だと結構効いてきそうですよね。

CPWの損失は3つの要因に分解できる。周波数が上がるほど全部が効いてくるから、ミリ波では1つも無視できない。

全損失 $\alpha_{\text{total}}$ は以下の3成分の和で表される。

1. 導体損失 $\alpha_c$

表皮効果により高周波電流が導体表面に集中し、実効抵抗が増加する。表皮深さ $\delta_s$ は次式で与えられる。

金(Au)の場合、$\sigma = 4.1 \times 10^7\,\text{S/m}$ で 10 GHz時に $\delta_s \approx 0.79\,\mu\text{m}$、77 GHzでは $\delta_s \approx 0.28\,\mu\text{m}$ まで薄くなる。導体厚さ $t$ は少なくとも $3\delta_s$ 以上が必要だ。

表面粗さも影響しますか?

非常に影響する。導体表面の粗さ(RMS値 $R_q$)が表皮深さと同程度になると、電流経路が長くなって抵抗が増える。Hammerstad-Jensenモデルでは補正係数 $K_{sr} = 1 + \frac{2}{\pi}\arctan\!\left(1.4\left(\frac{R_q}{\delta_s}\right)^2\right)$ を導体損失に掛ける。mmWave帯では $R_q$ が0.1μm違うだけで挿入損失が0.5 dB/cm変わることもあるよ。

2. 誘電体損失 $\alpha_d$

$\tan\delta$ は基板の誘電正接(損失角の正接)。低損失基板の選択が重要で、代表的な値を以下に示す。

| 基板材料 | $\varepsilon_r$ | $\tan\delta$(@10 GHz) | 用途 |

|---|---|---|---|

| 石英(Fused Silica) | 3.78 | 0.0001 | 高精度フィルタ |

| アルミナ(Al₂O₃) | 9.8 | 0.0003 | MMIC基板 |

| GaAs | 12.9 | 0.0006 | RFIC |

| Rogers RO4003C | 3.55 | 0.0027 | PCB高周波回路 |

| FR-4 | 4.4 | 0.02 | 低周波のみ(GHz帯は不適) |

3. 放射損失 $\alpha_r$

CPWの不連続部(ベンド、T分岐、ギャップ不整合)から電磁波が基板内部に放射される。特に $\varepsilon_r$ が高い基板では表面波モードが励起されやすく、隣接回路へのクロストークの原因になる。放射損失は周波数の2乗に比例して増大し、mmWave帯では支配的になることがある。

CPWの派生構造

CPWにもいろいろ種類があるって聞いたんですけど、どう使い分けるんですか?

主要な派生構造は3つある。設計目的によって使い分けるんだ。

| 構造 | 特徴 | メリット | 用途 |

|---|---|---|---|

| CBCPW (Conductor-Backed CPW) | 基板裏面にもGND | 放熱性向上、機械的強度 | パワーアンプ、パッケージ内配線 |

| FGCPW (Finite-Ground CPW) | GND幅を有限に制限 | 小型化、隣接回路との分離 | MMIC、高密度集積回路 |

| CPW + エアブリッジ | GND間をブリッジで接続 | スロットラインモード抑制 | MMICのT分岐、ベンド |

特にCBCPW(裏面GND付き)はシミュレーションで注意が必要だ。裏面GNDと表面GNDの間で平行平板モードが励起されて、本来のCPWモードと結合してしまう。これを防ぐために、エアブリッジやビアフェンスでGND同士を短絡する設計が必須になる。

CPW誕生の裏話 -- 1969年、ビアが嫌いだったC.P.Wen

コプレーナ導波路は1969年にC.P.Wenが発明した。当時はマイクロストリップ全盛期だったが、GaAs FETとの接続にビアを使うと寄生インダクタンスが問題になっていた。「GNDを同じ面に持ってくれば、ワイヤボンドで直接つなげるじゃないか」という発想がCPWの出発点だ。今ではフリップチップ実装やオンウェハーS-パラメータ測定の標準構造として不動の地位を築いている。50年以上経っても現役という、RF回路設計の世界では珍しいロングセラー構造だ。

数値解法と実装

FEM定式化と辺要素

CPWの電磁界シミュレーションって、普通のFEM(構造解析のやつ)とは何が違うんですか?

最大の違いは辺要素(Nedelec要素)を使うことだ。構造解析の節点要素だと、電磁場の接線連続性を保証できなくてスプリアス解(物理的に存在しない擬似的な固有モード)が大量に出てしまう。辺要素は各辺上の接線成分を自由度として持つから、$\nabla \cdot \mathbf{B} = 0$ を自然に満たせる。

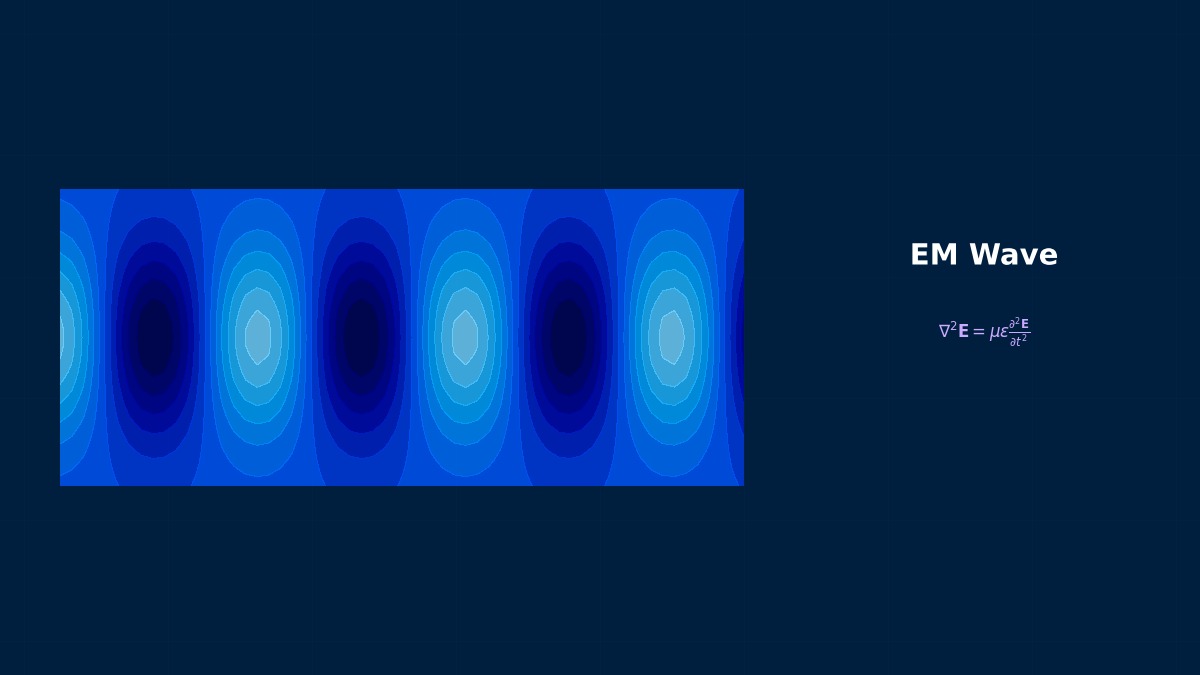

CPWの3D全波解析では、マクスウェル方程式からベクトル波動方程式を導出し、これを弱形式に変換して離散化する。

Galerkin法により弱形式化すると、試験関数 $\mathbf{W}_i$(辺要素の基底関数)を用いて:

これを行列形式に組み立てると:

ここで $[S]$ はカール-カール行列、$[T]$ は質量行列、$\{e\}$ は辺上の電界係数ベクトルである。

Ansys HFSSが「適応メッシュ」で有名ですけど、あれはどういう仕組みですか?

HFSSの適応メッシュリファインメント(AMR)は、解いた結果からエラーインジケータ(電界の不連続性)を評価して、誤差の大きい要素を自動的に細分化する。CPWではギャップ端部に電界が集中するから、そこだけが細かくなる。手動でメッシュを設計するより効率がいいし、$\Delta S$(Sパラメータの変化量)が閾値以下になるまで繰り返すから、収束保証もある。ただし「収束した」=「正しい」ではないから、独立した検証は必ず必要だ。

FDTD法によるCPW解析

FDTD法ってCST Studio Suiteで使われてますよね。FEMとどう使い分けるんですか?

FDTDは時間領域の手法で、1回のシミュレーションで広帯域の周波数応答を一気に取得できるのが最大のメリット。FEMは1周波数ずつ解くから、広帯域スイープだと計算量が膨れやすい。ただしFDTDは直交格子(Yeeセル)なので、斜めのジオメトリや曲面は階段近似になる。CPWのような矩形断面には相性がいい。

Yeeセルにおける電界・磁界の更新式(1D簡略版):

安定条件としてCourant条件を満たす必要がある。

CPWのFDTDで注意すべきなのはセルサイズだ。ギャップ幅 $s$ の中に少なくとも5〜10セルを配置しないとインピーダンスの精度が出ない。$s = 20\,\mu\text{m}$ なら $\Delta x \leq 4\,\mu\text{m}$ になるから、解析領域全体のセル数が膨大になりがちだ。サブグリッディングや非一様メッシュの活用が実務的に重要だよ。

MoM法(プレーナー構造特化)

Keysight ADSのMomentumとかSonnetってMoM法ですよね。CPWに向いてるんですか?

MoM(モーメント法)はプレーナー構造に特化した手法だ。CPWの導体面だけをメッシュで切って、基板はグリーン関数で厳密に扱う。つまり誘電体のメッシュが要らないから、FEMやFDTDよりも圧倒的にメッシュ数が少なくて済む。

特にSonnetは「ボックスモード」で解析領域を完全遮蔽して、スペクトル領域グリーン関数を使う。精度検証の論文も多くて、CPWのSパラメータ精度では定評がある。

MoMでは導体上の表面電流密度 $\mathbf{J}_s$ を基底関数 $\mathbf{f}_n$ で展開する。

試験関数との内積から連立方程式(インピーダンス行列)を構築する。

ポート励振とSパラメータ抽出

シミュレーションでSパラメータを取るとき、ポートの設定って重要ですか?

ポート設定はCPWシミュレーションで最も結果に影響する設定の1つだ。主に2種類ある。

- Wave Port:導波管モードを固有値解析で求める。正確だが、ポート面の境界条件(PEC/PMC/radiation)に結果が依存する。HFSSのデフォルト。

- Lumped Port:2点間に電圧源を定義する簡易的な方法。手軽だが、モード純度が低く高周波で不正確になりやすい。

CPWのWave Portでは、GND面をポート面の左右の端まで十分に広げないと、正しいCPWモードが励起されずにスロットラインモードが混入する。ポート幅はGND幅の5倍以上が目安だ。

ポート設定のたとえ

Wave Portは「楽器のマウスピース」のようなもの。形状を正しく設定しないと、意図しない倍音(スプリアスモード)が混じった不正確な音(Sパラメータ)が出てしまう。Lumped Portは「指で弦を弾く」ようなもの -- 手軽だが、常にきれいな音が出るとは限らない。

実践ガイド

モデリングワークフロー

CPWのシミュレーションを実際にやるとき、どういう手順で進めればいいですか?

基本的なフローは以下の5ステップだ。

- 寸法設計 — 目標インピーダンス(通常50 Ω)から $w$, $s$ を解析式で概算

- 3Dモデル構築 — 基板、導体(信号線+GND)、ポートを作成

- 材料・境界条件設定 — 基板の $\varepsilon_r$, $\tan\delta$、導体の $\sigma$、PML/ABCを設定

- メッシュ生成+ソルバー実行 — 適応メッシュまたは手動メッシュで解析

- 結果検証 — Sパラメータ、特性インピーダンス、電界分布を確認

最初の寸法設計で50 Ωにするには、具体的にどうすればいいですか?

たとえばアルミナ基板($\varepsilon_r = 9.8$、$h = 635\,\mu\text{m}$)で50 Ωを実現するなら、$w = 75\,\mu\text{m}$、$s = 45\,\mu\text{m}$ あたりが出発点になる。解析式で概算した後、シミュレーションで微調整するのが定石だ。GaAs基板($\varepsilon_r = 12.9$)だと $w$ をもう少し狭くする必要がある。

メッシュ戦略

CPWのメッシュで特に気をつけるべきポイントはどこですか?

CPWで電界が集中する場所は3箇所ある。ギャップの端部(信号線のエッジ)、導体の角、そして不連続部(ベンド、T分岐など)。この3箇所に重点的にメッシュを配置する。

| 領域 | 推奨メッシュサイズ | 理由 |

|---|---|---|

| ギャップ端部(信号線エッジ) | $s/10$ 以下 | 電界の特異的集中($E \propto r^{-1/3}$) |

| 導体厚さ方向 | $t$ を3層以上に分割 | 表皮効果の電流分布を解像 |

| 基板内部(電界が穏やか) | $\lambda_g / 10$ 以下 | 波長解像の基本条件 |

| PML/ABC領域 | $\lambda_0 / 6$ 程度 | 吸収境界の精度確保 |

| GND面(遠方) | 粗くてOK | 電流密度が低い |

メッシュ収束の目安としては、$\Delta S_{11}$ が連続する2回のリファインメントで0.02以下、かつ $Z_0$ の変化が1 Ω 以下なら十分だ。ただし損失(挿入損失 $S_{21}$)はインピーダンスより収束が遅いから、精度が必要なら追加リファインメントを検討してくれ。

境界条件とABC/PML

解析領域の外側はどう扱えばいいですか? 電磁波が漏れ出しますよね?

3つの方法がある。用途で使い分けるんだ。

- PEC/PMC壁 — 電磁波を完全反射する。パッケージ内部やシールド構造の再現に使う

- ABC(吸収境界条件) — 1次のMur ABCなど。計算軽量だが斜め入射の吸収性能が低い

- PML(完全整合層) — 理論上反射ゼロの吸収層。高精度だが層の厚さとメッシュが追加で必要

CPWの場合、基板の横方向と上方向にPMLまたはradiationバウンダリを設定する。GND面が十分広ければ側面はPECでもOKだが、GND幅が有限な場合は側面もPML推奨。PMLの外壁から導体までの距離は最低 $\lambda_0/4$ は確保してくれ。

デエンベディングとキャリブレーション

シミュレーション結果と実測を比較するとき、「デエンベディング」が必要って言われたんですけど、あれは何ですか?

デエンベディングは、デバイス以外の寄生成分(フィードライン、プローブパッド、コネクタ)の影響を除去する手法だ。シミュレーションでも測定でも、DUT(デバイス・アンダー・テスト)の前後にフィードラインがあるから、その分のSパラメータを引き算する必要がある。

代表的な方法は2つ。

- ポートデエンベディング(HFSSの"Deembed"機能) — ポートから指定距離だけ伝搬遅延を引き算。均一線路の場合に有効

- TRL(Thru-Reflect-Line)キャリブレーション — Thru、Open/Short、Line の3種類の校正標準をシミュレーションまたは測定で作成し、誤差行列を求める。最も高精度

TRLキャリブレーションって、シミュレーションでもやるんですか? 測定だけの話かと思ってました。

シミュレーションでもやるよ。特にパッケージ内のCPW-マイクロストリップ変換やワイヤボンド遷移を含む構造では、フィードCPW部分の影響を正確に除去するためにTRLデエンベディングをシミュレーション上で実行する。こうすることで「遷移部分だけ」のSパラメータが正確に取得できる。

CPWと5G mmWave基板 -- ギャップ幅10μmの世界

5Gの28 GHz帯・39 GHz帯向けフロントエンドモジュールでは、CPWのギャップ幅がわずか10〜20 μmになることも珍しくない。この領域ではフォトリソグラフィの精度限界とシミュレーション精度が直結する。製造誤差 ±2 μmがインピーダンスに数 Ω 影響し、リターンロスが設計値から外れる。実務ではモンテカルロ法による統計的シミュレーションで製造ばらつきへの感度を事前評価し、設計マージンを確保するのが当たり前になっている。

ソフトウェア比較

Ansys HFSS

HFSSがCPW解析の定番って聞きますけど、具体的にどこが強いんですか?

HFSSの最大の強みは適応メッシュリファインメント(AMR)だ。周波数領域FEMで、$\Delta S$ が収束するまで自動的にメッシュを細分化してくれる。CPWのような単純構造なら、ほぼデフォルト設定で正確な結果が出る。

CPW解析の手順は:

- Electronics Desktopで「HFSS Design」を選択

- 基板(Box)+信号線(Rectangle)+GND面(Rectangle × 2)を作成

- Wave Portを両端に設定(Integration Line をGNDから信号線へ引く)

- Radiation Boundary を解析領域外壁に設定

- Solution Setup で周波数範囲、Max Delta S、Max Passes を指定

- Analyze → Sパラメータ、$Z_0$、電界分布を確認

注意点として、Wave PortのIntegration Lineは信号線の中心からGNDの端まで引くこと。左右対称に2本引くか、1本だけ引いてモード1のみ使うかで結果が変わる場合がある。

CST Studio Suite

CST Studioは時間領域(FDTD)が得意ですよね。CPWに向いてますか?

CST の Time Domain Solver は、1回の時間パルス励振で広帯域のSパラメータをFFTで取得できる。CPWの広帯域特性評価(DC〜100 GHz とか)には非常に効率的だ。Hexahedral メッシュとの相性もいい。

ただし注意点がある。CPWのギャップが狭い場合、ギャップ内のメッシュセル数を確保するために全体のセル数が爆発しやすい。サブグリッディング(Local Mesh Properties)でギャップ周辺だけ細かくするのが実務的なコツだ。

COMSOL Multiphysics

COMSOLは「マルチフィジックス」が売りですけど、CPW単体でも使えますか?

もちろん使える。RF Moduleの「Electromagnetic Waves, Frequency Domain」インターフェースでCPWを解析できる。COMSOLの強みはマルチフィジックス連成だ。例えば高出力アンプのCPWで「電磁界 → ジュール発熱 → 熱膨張 → 寸法変化 → インピーダンス変動」という連鎖を1つのモデルで解ける。

ただしHFSSやCSTほどRF専用のウィザードが充実していないから、ポート設定やデエンベディングは手動で構築する必要がある。FEMの基礎知識がある人向けだ。

OSSツール(OpenEMS・Meep)

商用ソフトは高額ですよね。無料で使えるツールはないんですか?

OSSだとOpenEMS(FDTD、MATLAB/Octave連携)とMeep(MIT開発のFDTD)が代表的だ。どちらもCPWの解析は可能で、学術論文での使用例もある。ただしGUIが限定的で、モデル構築はスクリプトベースになる。ポストプロセッサも商用ツールほど充実していないから、ParaViewなどを併用することが多い。

研究室レベルや学習用途には十分だけど、製品設計の品質保証(QA)ドキュメントで「OSSで検証しました」が通るかは会社の文化による。商用ツールとのクロスバリデーションに使うのが現実的だ。

機能比較マトリクス

| 機能 | HFSS | CST | COMSOL | Momentum | Sonnet | OpenEMS |

|---|---|---|---|---|---|---|

| 解法 | FEM(周波数) | FDTD / FEM | FEM(周波数) | MoM | MoM | FDTD |

| 適応メッシュ | ○(AMR) | ○ | ○ | △ | × | × |

| マルチフィジックス | △ | △ | ○ | × | × | × |

| 回路コシミュレーション | ○ | ○ | △ | ○ | △ | × |

| パラメトリック解析 | ○ | ○ | ○ | ○ | ○ | ○(スクリプト) |

| GPU加速 | ○ | ○ | △ | × | × | × |

| ライセンス費用 | 高 | 高 | 中〜高 | 高(ADS同梱) | 中 | 無料(GPL) |

結局、CPWだけやるならどれがいいですか?

用途で選ぶ。MMIC/RFIC設計フローの中で使うならHFSSかMomentum(ADS)。広帯域の過渡解析が必要ならCST。熱や応力との連成が必要ならCOMSOL。プレーナー回路の精度検証ならSonnet。学習・研究ならOpenEMS。万能なツールは存在しないから、目的に合ったものを選ぶのが正解だ。

ADS Momentum vs. Sonnet -- RF設計者の「きのこたけのこ」論争

CPW設計で使われるMoMシミュレータの2大勢力がKeysight ADSのMomentumとSonnet Softwareだ。Momentumは回路シミュレーションとの統合が強く、RFフローの中でシームレスにコシミュレーションできる。一方SonnetはRF/マイクロ波特化で精度検証の論文実績が多く、プレーナー回路(CPW、マイクロストリップ、スパイラルインダクタ)の精度に定評がある。RF設計者の間では「どっち派?」の話題がよく出るが、予算と既存フローに合わせて選ぶのが実務の常識で、正解は1つではない。

トラブルシューティング

インピーダンスが合わない

シミュレーションで50 Ωに設計したのに、実際に作ったら45 Ωになっちゃいました。何が原因ですか?

CPWで「インピーダンスが合わない」のはよくあるトラブルだ。チェックすべきポイントを優先度順に挙げる。

| 原因 | 影響の大きさ | チェック方法 | 対策 |

|---|---|---|---|

| 基板の $\varepsilon_r$ がデータシートと異なる | 大 | リング共振器法で実測 | 実測値でシミュレーション再実行 |

| エッチングによるギャップ幅変化 | 大 | SEM/光学顕微鏡で実測 | 製造公差を含めたパラメトリック解析 |

| 導体厚さ $t$ の考慮不足 | 中 | プロファイラで実測 | 有限厚モデルで再解析 |

| ポート設定の不備 | 中 | ポート幅・高さを変えて感度確認 | Wave Port を十分な大きさに |

| GND幅が有限でモード変化 | 小〜中 | GND幅を変えてスイープ | GND幅を $5(w+2s)$ 以上に |

経験的に最も多いのは「基板の $\varepsilon_r$ がカタログ値と違う」パターンだ。特にPCB材料は製造ロットや周波数で $\varepsilon_r$ が変わる。10 GHz以上ではカタログ値(通常1 MHzで測定)をそのまま使うと確実にズレる。基板メーカーから周波数別の $\varepsilon_r$ データを入手するか、自分でリング共振器テストで実測するのが鉄則だ。

スプリアスモードの発生

Sパラメータに変なディップ(notch)が出るんですけど、あれは何ですか?

典型的な原因はスプリアスモードの励起だ。CPWには本来のCPWモード(奇モード)以外に、スロットラインモード(偶モード)と平行平板モード(CBCPWの場合)が存在する。これらが不連続部で結合すると、特定周波数で共振してディップが現れる。

- スロットラインモード抑制 → エアブリッジまたはボンドワイヤでGND間を短絡。間隔は $\lambda_g/4$ 以下

- 平行平板モード抑制 → ビアフェンスで表面GNDと裏面GNDを $\lambda_g/10$ 間隔で接続

- 基板モード抑制 → 基板厚さを薄くする、または溝(trench)を切る

収束しない・計算が終わらない

HFSSの適応メッシュが全然収束しなくて、Passを増やしても $\Delta S$ が下がりません。

考えられる原因と対策を挙げる。

- ポート面が小さすぎる — CPWモードがポート面に収まっていない。ポートの高さと幅をGND幅の5倍以上に拡大

- 解析領域が狭すぎる — 放射波がPML到達前に反射。解析領域を $\lambda_0/2$ 以上拡張

- 共振構造になっている — 解析周波数が構造の共振点に近いと、わずかなメッシュ変化でSパラメータが大きく変動する。共振周波数を避けて収束確認し、その後共振帯に戻る

- 初期メッシュが粗すぎる — ギャップに要素が1〜2個しかない。Initial Meshでギャップ内に最低5要素を手動設定

CSTのFDTDで計算時間が異常に長い場合は?

FDTDで計算時間が爆発する原因は主に2つ。1つ目はセル数が多すぎる(ギャップに細かいメッシュを入れた結果、Courant条件で時間ステップが極小になる)。サブグリッディングで解決できる。2つ目はエネルギーがなかなか減衰しない(高Q共振器や低損失構造)。この場合は Auto-Regressive(AR)フィルタを有効にして、時間信号を早期打ち切り+外挿する設定にするといい。

測定との相関が取れない

シミュレーションと測定で、低周波は合うのに高周波でズレるんです。

高周波になるほど「シミュレーションで無視した要因」が効いてくるパターンだ。チェックリストを示す。

- 表面粗さ — Hammerstad-Jensenモデルまたは修正Morgan粗さモデルをシミュレーションに入れているか?

- $\varepsilon_r$ の周波数依存性 — 広帯域ではDjordjevic-Sarkarモデル等で $\varepsilon_r(f)$ を表現する必要がある

- プローブのランチパッド — G-S-Gプローブのランチパッドの寄生容量をモデルに含めているか?

- キャリブレーション品質 — 測定側のTRL/SOLT校正は適切か? 校正基準器のS-パラメータファイルは最新か?

- 放射損失 — シミュレーションで放射境界を使っているか? PEC壁だと放射損失が反映されない

最後に1つ鉄則を教えておく。「シミュレーションが間違っている」と決めつける前に、まず測定系の問題を徹底的に排除すること。ケーブルの緩み、プローブの接触不良、校正の劣化 -- これらが原因の「偽の不一致」は実務で本当に多い。特にmmWave帯では、プローブを基板に着地させる圧力が0.5 mil違うだけで $S_{11}$ が数dB変わることもある。

CPWシミュレーション:初心者が陥りやすい落とし穴

- 「解析式で50 Ωだからシミュレーション不要」 — 解析式は無限薄導体・無限GNDの理想モデル。実際は導体厚さ、有限GND、基板端部で数 Ω ずれる

- 「GND面は電位ゼロだからメッシュ不要」 — GND上にも表面電流が流れる。特にギャップ近傍のGND端部は電流密度が高い

- 「2Dで十分」 — ベンドやT分岐の3D放射効果、パッケージ内のモード結合は2Dでは見えない

- 「Lumped Port で十分」 — GHz帯以上ではWave Port推奨。Lumped Portはモード純度が低い

なった

詳しく

報告