マイクロストリップ線路の電磁界解析

理論と物理

マイクロストリップ線路とは

マイクロストリップラインって要するにプリント基板の配線パターンですよね? なぜ電磁解析が必要なんですか?

いい質問だね。低周波のデジタル回路なら配線は単なる「つなぎ」で済む。でもGHz帯になると波長が基板サイズと同程度になり、配線が伝送線路として振る舞うんだ。インピーダンス不整合があると信号が反射して波形が乱れる。

具体的にどのくらいシビアなんですか?

例えばUSB 3.2やPCIe Gen5では90 $\Omega$ 差動インピーダンスを $\pm 5\%$ 以内に管理する必要がある。これを外すとアイパターンが閉じてビットエラーが増える。5G基地局のRFフロントエンドなら50 $\Omega$ を $\pm 2\%$ で狙うこともある。だから電磁界シミュレーションが不可欠なんだ。

マイクロストリップ線路は、誘電体基板の片面に導体ストリップ、反対面にグランドプレーンを配置した平面型の伝送線路構造である。PCB(プリント基板)やMMIC(モノリシックマイクロ波集積回路)で最も広く使われる。

構造がオープン(上面が空気に露出)なため、純粋なTEMモードは支持できず、準TEMモード(quasi-TEM)が伝搬する。低周波ではTEM近似が成り立つが、周波数が上がるとTE/TM成分が無視できなくなり分散が生じる。

特性インピーダンスの理論式

じゃあ、そのインピーダンスってどうやって計算するんですか? CADツールがいきなり必要?

まず手計算で使える近似式がある。Hammerstad-Jensen(1980)の式が実務で最も使われていて、$w/h > 1$ と $w/h \leq 1$ で場合分けする。精度は $\varepsilon_r \leq 16$、$0.05 \leq w/h \leq 20$ の範囲で約1%以内だ。

狭い線路($w/h \leq 1$)の場合:

広い線路($w/h > 1$)の場合:

また、導体厚 $t$ を含むIPC-2141準拠の簡易式も広く使われる:

FR4基板で50 $\Omega$ にするには、具体的にどのくらいの線路幅にすればいいんですか?

FR4($\varepsilon_r \approx 4.3$)で基板厚 $h = 0.2\,\text{mm}$、銅箔厚 $t = 35\,\mu\text{m}$ だと、$w \approx 0.36\,\text{mm}$ で50 $\Omega$ になる。$w/h \approx 1.8$ だから広い線路の式を使うわけだ。実務では2D断面ソルバー(例えばSIwave)で検証するのが定番だけどね。

実効誘電率と分散

式に出てくる $\varepsilon_{eff}$ って何ですか? 基板の誘電率 $\varepsilon_r$ とは違うんですか?

マイクロストリップは電界が誘電体と空気の両方にまたがっているから、電磁波が「感じる」誘電率は $\varepsilon_r$ と1(空気)の中間の値になる。これが実効誘電率 $\varepsilon_{eff}$ だ。

例えばFR4($\varepsilon_r = 4.3$)で $w/h = 2$ のとき、$\varepsilon_{eff} \approx 3.3$ となる。これにより伝搬速度は $v = c/\sqrt{\varepsilon_{eff}} \approx 1.65 \times 10^8\,\text{m/s}$ と、真空中の約55%に低下する。

しかし周波数が上がると電界がより多く誘電体に集中するため、$\varepsilon_{eff}$ は周波数とともに $\varepsilon_r$ に漸近する。この分散(dispersion)を記述するKirschningの周波数依存式:

ここで $f_p = Z_0 / (2\mu_0 h)$ は周波数パラメータ、$G$ はジオメトリ依存の定数である。この分散により、パルス信号の高周波成分が遅延し、エッジが鈍るISI(符号間干渉)が生じる。

損失メカニズム

実際の基板では信号が減衰しますよね。損失にはどんな種類があるんですか?

大きく分けて3つある。導体損失、誘電体損失、放射損失だ。低GHz帯では導体損失が支配的で、10 GHzを超えると誘電体損失が効いてくる。

導体損失($\alpha_c$)は表皮効果により周波数の平方根に比例して増大する:

ここで $R_s$ は表面抵抗、$\sigma$ は導電率(銅: $5.8 \times 10^7\,\text{S/m}$)。さらに現実の銅箔には表面粗さがあり、Hammerstad-Bekkadal補正で $R_s$ を1.4〜2倍に増大させる必要がある。

誘電体損失($\alpha_d$)は誘電正接 $\tan\delta$ で記述される:

| 基板材料 | $\varepsilon_r$ | $\tan\delta$ | 用途 |

|---|---|---|---|

| FR4 | 4.2〜4.5 | 0.02 | 一般デジタル(〜3 GHz) |

| Megtron 6 | 3.7 | 0.002 | 高速デジタル(〜25 GHz) |

| Rogers RO4003C | 3.55 | 0.0027 | RF/マイクロ波 |

| Rogers RT/duroid 5880 | 2.20 | 0.0009 | ミリ波(77 GHz車載レーダー) |

| アルミナ($\text{Al}_2\text{O}_3$) | 9.8 | 0.0001 | MMIC基板 |

支配方程式

CAEで解く「方程式」って、結局マクスウェル方程式ですか?

その通り。全ての電磁界解析の出発点はマクスウェル方程式だ。時間調和場($e^{j\omega t}$ 依存)を仮定すると周波数領域形式になる。

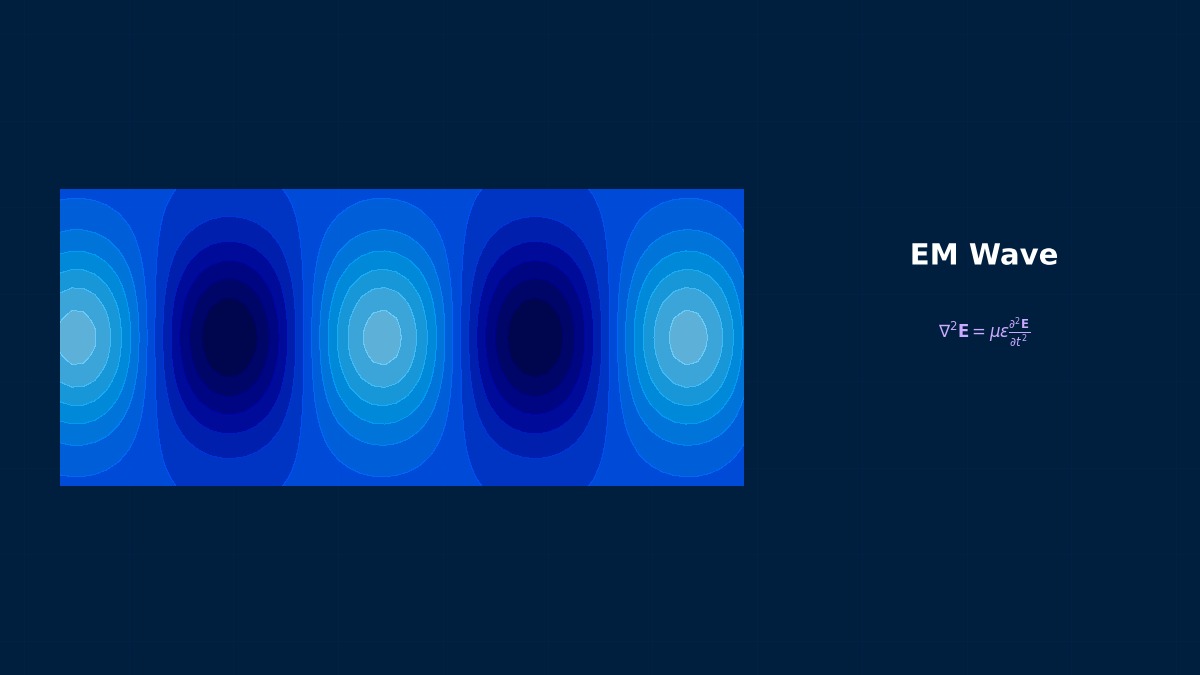

これを $\mathbf{E}$ について消去すると、ベクトル波動方程式が得られる:

ここで $k_0 = \omega\sqrt{\mu_0\varepsilon_0} = 2\pi f / c$ は自由空間波数。この方程式をFEM、FDTD、MoMなどの数値手法で離散化して解くのがマイクロストリップ線路の電磁界シミュレーションである。

「準TEMモード」という妥協の産物

マイクロストリップ線路は真のTEM波(縦波成分ゼロ)を支持しない。基板(誘電体)と空気の二媒質がある限り、TM成分が混在する「準TEMモード」が伝播する。特性インピーダンスはHammerstad-Jensenの近似式(1980)で精度1%以内で求められるが、高周波では分散が顕著になる。実は1970年代にはStriplineの方が電気特性は優れていたが、マイクロストリップは部品実装がしやすく、結局「物理的妥協」と「製造容易性」のトレードオフでマイクロストリップが勝利した。CAEではFEM・FDTD・MoMによる厳密解析が「分散特性」の実用評価に使われ、設計周波数での有効誘電率と損失を精密に見積もる。

各変数の物理的意味

- $w$(線路幅):導体ストリップの幅。$Z_0$ に最も影響する設計パラメータ。幅を広げるとインピーダンスが下がる(容量増大のため)。

- $h$(基板厚):誘電体基板の厚さ。厚くするとインピーダンスが上がり、放射損失も増加する。製造公差 $\pm 10\%$ が $Z_0$ を $\pm 5\%$ 変動させる。

- $\varepsilon_r$(比誘電率):基板材料固有の値。大きいほど線路を小型化できるが、損失と分散が増加する。

- $t$(導体厚):銅箔の厚さ(通常18〜35 $\mu$m)。$w/h$ が小さいとき $Z_0$ への影響が大きくなる。

- $\tan\delta$(誘電正接):誘電体の損失指標。FR4は0.02と大きく、Rogers系は0.001〜0.003と小さい。

近似式の適用限界

- 準TEM近似は $f \ll f_{TE1}$(最低次TEモードのカットオフ周波数)でのみ有効

- $f_{TE1} \approx c / (2w\sqrt{\varepsilon_r - 1})$ を超えると高次モードが励振し、近似式は使えない

- 線路間の結合(クロストーク)は単独線路の式では評価できない。結合線路解析が必要

- ビア・曲がり・テーパーなどの不連続部は3D電磁界解析が必須

- 基板材料の周波数依存性(Causal Dk/Df)を無視すると広帯域特性で誤差が大きくなる

数値解法と実装

FEMによる周波数領域解析

マイクロストリップの解析に使う数値手法って、どう使い分けるんですか?

大きく3つある。FEM(有限要素法)は周波数領域で1周波数ずつ解く。メッシュ適応(Adaptive Mesh Refinement)が自動で走るので、複雑な3D構造でも使いやすい。Ansys HFSSの主力エンジンだ。

FEMではベクトル波動方程式を弱形式に変換し、辺要素(Nedelec要素)で離散化する。周波数領域なので、各周波数ポイントで

という線形方程式系を解く。ここで $[S]$ はスティフネス行列($\nabla \times$ 演算子由来)、$[T]$ は質量行列($\varepsilon_r$ 由来)、$\{b\}$ はポート励振ベクトルである。

Ansys HFSSの自動メッシュ適応: Sパラメータの変化量 $|\Delta S_{ij}|$ が設定閾値(デフォルト0.02)以下になるまで、電界勾配の大きい領域のメッシュを自動的に細分化する。典型的には3〜6パス(メッシュ更新回数)で収束する。

FDTDによる時間領域解析

FDTDって、FEMとどう違うんですか?

FDTDは時間領域で直接マクスウェル方程式を時間進行させる。ガウスパルスを1回打ち込むだけで、FFT後に広帯域の周波数特性が一気に得られる。CST Studioの時間領域ソルバーがこれだ。

じゃあFDTDの方が効率的なんですか?

ケースバイケースだ。FDTDは直交格子(Yeeセル)を使うから、斜め構造の表現精度がメッシュに依存する。また、高Q構造(共振器など)だとリングダウンに時間がかかって計算が終わらない。一方で広帯域特性が一度で得られるのは強力な利点だ。

Yeeの差分スキーム(1966)は $\mathbf{E}$ と $\mathbf{H}$ を空間的・時間的に半格子ずらして配置する:

安定性条件(CFL条件): $\Delta t \leq \frac{1}{c\sqrt{1/\Delta x^2 + 1/\Delta y^2 + 1/\Delta z^2}}$

| 手法 | ドメイン | 得意な構造 | 不得意な構造 | 代表ツール |

|---|---|---|---|---|

| FEM | 周波数領域 | 複雑3D、曲面、非均質材料 | 超広帯域(多周波数点) | Ansys HFSS |

| FDTD | 時間領域 | 広帯域、過渡応答 | 高Q共振器、微細構造 | CST Studio |

| MoM | 周波数領域 | 平面構造、開放問題 | 3D体積構造 | Sonnet, Momentum |

| 2.5D Planar | 周波数領域 | 多層基板、高速設計 | 3D不連続部 | Ansys SIwave |

MoMとPlanar 3D

MoMっていうのもよく聞きますが、マイクロストリップとの相性はどうなんですか?

MoM(モーメント法)は平面構造に非常に強い。グリーン関数を使って導体面の電流分布を直接求めるから、空気領域のメッシュが不要で効率がいい。Sonnet SuiteやKeysight Momentumがこの方式だ。PCB設計者向けには「Planar 3D」と呼ばれる2.5D手法が人気で、多層基板の各層を平面問題として扱い、ビアで層間を接続する。SIwaveやCadence Clarity 3Dがこれに該当する。

辺要素とスプリアスモード

さっき「辺要素」って出てきましたけど、普通の有限要素と何が違うんですか?

通常の節点要素(スカラー変数を節点に割り当て)で電磁場を解くと、物理的に存在しない偽の解(スプリアスモード)が大量に発生するんだ。辺要素(Nedelec要素)はベクトル場の接線成分を辺に割り当てることで、$\nabla \cdot \mathbf{B} = 0$ を自動的に満たし、スプリアスモードを排除する。高周波FEMでは辺要素が事実上の標準だ。

周波数領域 vs 時間領域の使い分け

周波数領域解析は「ラジオの特定の周波数に合わせる」ようなもの――1つの周波数での応答を効率的に計算できる。時間領域解析は「全チャンネルを同時に録画する」ようなもの――あらゆる周波数成分を含む過渡現象を再現できるが計算コストが高い。マイクロストリップのSパラメータを10周波数点だけ欲しいならFEM、DC〜40 GHzのフルバンドが必要ならFDTDが効率的だ。

実践ガイド

解析フロー

実際にマイクロストリップを解析するとき、最初に何から始めるべきですか?

基本フローは5ステップだ。ポイントは最初に手計算で目標値を出しておくこと。いきなり3D解析に飛び込むと、結果の正しさを検証できなくなる。

- 仕様の明確化:目標インピーダンス、周波数帯域、挿入損失上限、基板スタックアップを確定

- 手計算/2Dソルバーで初期設計:Hammerstad式やSIwaveで線路幅 $w$ を決定

- 3Dモデリング:ビア、コネクタ、テーパー等の不連続部を含めたモデルを作成

- 電磁界シミュレーション実行:Sパラメータ、電界分布、TDRインピーダンスプロファイルを取得

- ポスト処理と設計反復:アイダイアグラムシミュレーション、感度解析、最終検証

メッシュ設計の要点

メッシュってどのくらい細かくすればいいんですか?

マイクロストリップ特有のメッシュ要件がある。導体エッジは電界が特異的に集中するから、エッジ付近を最小波長 $\lambda_{min}$ の $1/20$ 以下にする。また基板厚方向には最低4〜6層のメッシュが必要だ。表皮深さ $\delta$ よりも細かいメッシュで導体損失を評価するのも忘れずに。

| 領域 | 推奨メッシュサイズ | 理由 |

|---|---|---|

| 導体エッジ付近 | $\lambda_{min}/20$ 以下 | 電界集中の正確な評価 |

| 基板厚方向 | 4〜6層 | $\varepsilon_{eff}$ の精度確保 |

| 導体内部(損失評価時) | 表皮深さ $\delta$ 以下 | 表面電流密度の精度 |

| グランドプレーン上 | $\lambda_{min}/10$ | 戻り電流パスの評価 |

| 放射境界付近 | $\lambda_{min}/6$ | PML/ABCの精度 |

10 GHzの設計だと具体的にはどのくらいのサイズになりますか?

FR4で $\varepsilon_{eff} \approx 3.3$ だと $\lambda_{min} = c/(f\sqrt{\varepsilon_{eff}}) \approx 16.5\,\text{mm}$。エッジ付近は $16.5/20 \approx 0.8\,\text{mm}$ 以下にする。銅の表皮深さは10 GHzで約0.66 $\mu$m だから、導体損失まで正確に出したいなら、導体内メッシュは $\mu$m オーダーが必要になる。ここがマイクロストリップ解析の計算コストが高い理由の一つだ。

境界条件とポート設定

境界条件の設定で注意すべき点は何ですか?

マイクロストリップ解析では3つの境界条件が重要だ。まずポート(Waveport or Lumped port)の設定。次に放射境界条件(PMLまたはABC)で開放空間を模擬する。最後にグランドプレーンのPEC(完全導体)条件だ。

- Waveport: 2D固有値問題を解いてモードパターンを自動計算。正確だが、ポート面が解析領域の境界面上にある必要がある。HFSSの標準

- Lumped Port: 導体間に電圧源を定義。配置が柔軟だが、高周波での精度はWaveportに劣る

- PML(完全整合層): 理論上は任意の入射角で無反射吸収。HFSSではデフォルト。PMLの厚さは $\lambda/4$ 以上を推奨

- 放射境界(ABC): 計算コストが低いが、PMLより反射が大きい。境界を解析対象から $\lambda/4$ 以上離す

検証とバリデーション

シミュレーション結果が正しいかどうか、どうやって確認するんですか?

5段階の検証プロセスがある。特にマイクロストリップではSパラメータの相反性($S_{12} = S_{21}$)とパッシビティ($|S_{11}|^2 + |S_{21}|^2 \leq 1$)の確認が基本中の基本だ。

- メッシュ収束確認: AMRパスごとのSパラメータ変化が $|\Delta S| < 0.01$ であること

- 相反性チェック: $|S_{12} - S_{21}| < -60\,\text{dB}$(パッシブ構造の場合)

- パッシビティチェック: 全周波数で $\sum|S_{ij}|^2 \leq 1$

- 解析式との照合: 直線区間の $Z_0$ がHammerstad式と$\pm 3\%$ 以内で一致

- 実測データとの比較: VNA(ベクトルネットワークアナライザ)でのSパラメータ測定との照合。校正(TRL/SOLT)の精度にも注意

基板厚ばらつきの罠

FR4基板の厚さ公差は一般に $\pm 10\%$ だが、特性インピーダンスへの影響は設計者に見落とされがちだ。例えば50 $\Omega$ 設計のマイクロストリップで基板厚が10%薄くなると、実インピーダンスは約54 $\Omega$ に上昇する。反射係数 $\Gamma = (54-50)/(54+50) \approx 0.04$、つまり $-28\,\text{dB}$ のリターンロス。これは高速設計では問題になりうる。CAEの感度解析(パラメトリックスイープ)で基板厚・誘電率・銅箔厚の公差を同時変動させ、インピーダンス変動量を統計的に評価するのが量産設計の必須ステップになっている。

初心者が陥りやすい落とし穴

「マイクロストリップの解析でよくある失敗第1位はポートの設定ミスです。Waveportの面積が小さすぎるとモードパターンが正しく計算できず、$Z_0$ が基準値からずれます。ポート面は線路幅の5〜10倍の幅、基板厚の8〜10倍の高さを確保してください。第2位は放射境界が近すぎること。マイクロストリップはオープン構造なので電磁界が上空に広がります。PMLや放射境界を導体から $\lambda/4$ 以上離さないと、反射波が結果を汚染します。

ソフトウェア比較

主要ツール一覧

マイクロストリップの解析に使えるツールって、どんなものがありますか?

用途によって3つのカテゴリに分かれる。3Dフルウェーブソルバー(HFSS、CST、COMSOL)、2.5D Planarソルバー(SIwave、Momentum、Sonnet)、回路シミュレータ連携(AWR、ADS)だ。

| ツール名 | 開発元 | 主要手法 | 強み |

|---|---|---|---|

| Ansys HFSS | Ansys Inc. | FEM(周波数領域) | 自動メッシュ適応、高精度3D解析 |

| CST Studio Suite | Dassault SIMULIA | FDTD / FEM / MoM | 広帯域、EMC/EMI、マルチソルバー |

| COMSOL Multiphysics | COMSOL AB | FEM(マルチフィジクス) | 電磁-熱-構造連成解析 |

| Ansys SIwave | Ansys Inc. | 2.5D FEM / MoM | PCB/パッケージ全体の高速解析 |

| Keysight ADS / Momentum | Keysight | MoM(Planar 3D) | RFIC/MMICフィルタ、マッチング |

| Sonnet Suite | Sonnet Software | MoM(FFTベース) | 平面構造の高精度解析、低コスト |

| Cadence AWR | Cadence | 回路+EM連成 | 回路設計との一体運用 |

| openEMS | OSS | FDTD | 無償、Octave/MATLAB連携 |

機能比較マトリクス

結局、どれが一番いいんですか?

「一番」は存在しない。用途によって最適解が変わる。

| 機能 | HFSS | CST | COMSOL | SIwave | Sonnet |

|---|---|---|---|---|---|

| 3D任意形状 | ◎ | ◎ | ◎ | △ | × |

| 自動メッシュ適応 | ◎ | ○ | ○ | ◎ | ○ |

| 広帯域解析(1回実行) | △ | ◎ | △ | △ | △ |

| 多層PCB対応 | ○ | ○ | ○ | ◎ | ◎ |

| 電磁-熱連成 | ○ | ○ | ◎ | ○ | × |

| スクリプト自動化 | ◎(Python) | ○(VBA) | ○(Java API) | ○ | △ |

| コスト | 高 | 高 | 中〜高 | 中 | 低〜中 |

選定の指針

予算が限られてる中小企業やスタートアップはどう選べばいいですか?

3つの軸で考えるといい。

- 「何を解くか」:PCBの配線インピーダンスだけならSIwaveで十分。コネクタやパッケージの3D構造まで含めるならHFSSかCST

- 「頻度と規模」:月に数回の解析ならSonnetの低コストライセンスが合理的。毎日大規模解析を回すならHFSSのHPC対応が必要

- 「エコシステム」:Cadence Allegroでボード設計しているならCadence系(Clarity 3D)、Ansys系のSI/PI設計環境ならSIwave+HFSSの連携が自然

openEMS ―― 無償で始めるマイクロストリップ解析

商用ツールに手が出ない学生や研究者には、オープンソースのopenEMSがおすすめだ。FDTDベースの3Dフルウェーブソルバーで、MATLAB/Octaveから直接モデルを定義・実行・可視化できる。AppCSXCADというGUIもある。マイクロストリップのチュートリアルが充実しており、Sパラメータ抽出やフィールドプロット、遠方界計算まで一通り体験できる。計算速度は商用ツールに劣るが、電磁界解析の原理を理解する教育用途としては最高の教材だ。

トラブルシューティング

よくある失敗と対策

先生、マイクロストリップの解析でハマりやすいポイントを教えてください。先輩が「徹夜デバッグした」って言ってたんですが...

あるあるだね(笑)。典型的なトラブルをまとめておこう。

| 症状 | 原因 | 対策 |

|---|---|---|

| $Z_0$ が理論値から $\pm 10\%$ 以上ずれる | ポートサイズ不足、メッシュ粗すぎ | Waveportを線路幅の5〜10倍に拡大、AMR収束確認 |

| $S_{11}$ が $-20\,\text{dB}$ 以上悪い(直線区間で) | ポートインピーダンス不整合 | de-embedding設定の確認、TDR波形でインピーダンスプロファイルを確認 |

| $S_{21}$ の損失が過大 | 導体損失の $\tan\delta$ 設定ミス、表面粗さ未考慮 | 材料パラメータの再確認、Huray/Hammerstad粗さモデルの適用 |

| パッシビティ違反($|S_{11}|^2 + |S_{21}|^2 > 1$) | メッシュ不足、PML設定ミス | メッシュ細分化、PML層数を増加(最低8層) |

| 高周波で異常なピーク/ディップ | 基板モード(パラレルプレートモード)の励振 | グランドビアの追加、解析領域サイズの確認 |

| 計算が終わらない(FDTD) | 高Q共振、エネルギー残留 | $-30\,\text{dB}$ エネルギー減衰基準に緩和、または周波数領域ソルバーに切り替え |

| メモリ不足 | 不必要に広い解析領域、導体内メッシュ過剰 | 対称面の活用($1/2$ モデル)、導体をインピーダンス境界条件で置換 |

ツール固有のエラー

HFSSを使っていて「Port refinement failed」ってエラーが出たんですが、何が悪いんですか?

ポート面のメッシュでモードパターンが計算できなかったということだ。ポートの面積が小さすぎるか、ポート面上に複数の導体が密集しているケースが多い。ポートサイズを拡大するか、Lumped Portに切り替えてみよう。

Ansys HFSS よくあるエラー:

- "Port refinement failed": ポート面でモード計算失敗 → ポートサイズ拡大、導体エッジのメッシュ細分化

- "Matrix solver failed to converge": 直接法メモリ不足 → 反復法(MUMPS → iterative)に切り替え

- "Passivity not enforced": Sパラメータのパッシビティ違反 → AMRパス数を増やす、最小メッシュサイズを指定

CST Studio よくあるエラー:

- "Energy has not decayed to -30 dB": FDTD時間積分で定常状態に未到達 → シミュレーション時間を延長、ポートインピーダンスを確認

- "Mesh cells exceed available memory": 直交格子が巨大化 → サブグリッディング活用、対称面で $1/2$ モデル化

- "Port mode solver warning": ポートモードの識別失敗 → ポートサイズ調整、基板外周にPECウォールを追加

デバッグの鉄則

- まず単純モデルで検証:問題の線路パターンをいきなり解析せず、まず直線の50 $\Omega$ マイクロストリップで設定の正しさを確認する

- Sパラメータの物理チェック:$S_{12} = S_{21}$(相反性)、$|S_{11}|^2 + |S_{21}|^2 \leq 1$(パッシビティ)が満たされなければメッシュかポートに問題がある

- 電界分布を可視化:数値だけ見ず、断面の電界コンターを表示する。想定外のモードが立っていないか確認

- 1つずつ変数を変える:メッシュ、ポート、PMLを同時に変えると原因特定が不可能になる。対照実験の原則を守る

関連トピック

なった

詳しく

報告